# **APPLICATION NOTE**

# PWM Generation with ST62 Auto-reload Timer

J.NICOLAI

# INTRODUCTION

This note presents how to use the ST62 Auto-reload Timer (ARTimer) for the generation of a PWM signal tunable in frequency and duty cycle. As example, the generation of a 30kHz PWM signal with duty cycle proportional to an analog input voltage is presented.

# **Auto-reload Timer description**

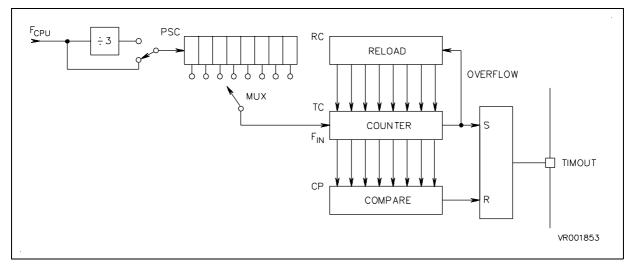

This timer is an 8 bit timer/counter with prescaler. It includes auto-reload PWM, capture and compare capability with one input and one output pins. It is controlled by the following registers (8 bit):

- Mode Control Register (MC)

- Status registers (SC0, SC1)

- Load register (LR)

- Incremental counter register (TC)

- Compare register (CP)

- Reload/Capture register (RC)

It can also wake the MCU from wait mode and exit from stop mode if an external event is present on the input pin. The prescaler ratio can be programmed to choose the timer input frequency  $F_N$  (see Table 1).

# Figure 1. Auto-reload Timer Block Diagram

# **Pulse Width Modulation (PWM) Generation**

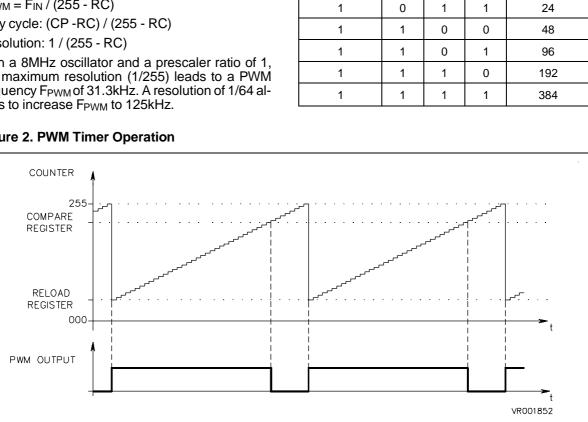

Using the PWM generation capability of the AR-Timer, the CPU of the microcontroller has only to start/stop the timer and update the duty cycle. High speed PWM signals in the range of 100kHz can be generated. The timer clock input frequency FIN can be selected by the oscillator clock fosc and the prescaler ratio. The PWM signal period is controlled by the Reload register. The duty cycle is defined by the Compare register CP (see Figure 2).

The register TC is incremented from RC to 255d, then reloaded at RC to count again. The PWM output is set on the overflow of TC and reset when TC=CP.

CP can have any value between RC and 255d. So RC should be minimal and the prescaler ratio as small as possible to achieve a maximum resolution.

Major formulae for PWM generation are:

$F_{IN} = f_{osc} / (prescaler ratio)$

$F_{PWM} = F_{IN} / (255 - RC)$

Duty cycle: (CP -RC) / (255 - RC)

Resolution: 1 / (255 - RC)

With a 8MHz oscillator and a prescaler ratio of 1, the maximum resolution (1/255) leads to a PWM frequency FPWM of 31.3kHz. A resolution of 1/64 allows to increase FPWM to 125kHz.

#### Figure 2. PWM Timer Operation

#### **Table 1. Prescaler Programming Ratio**

PS2

PS1

PS0

PRESCALER

Ratio

Bit 0

Reg. SC1

# Example 1:

Target: Generate a 12kHz PWM signal with a duty cycle of 37%, using an oscillator frequency of 4MHz: We want to generate a periodic signal at a frequency of 12 kHz and a duty cycle of 37%.

The CPU frequency (quartz frequency) is 4 MHz.

Let's try with a prescaler ratio of 3:

$F_{IN} = 4 MHz / 3 = 1333.33 kHz$

12 kHz = 1333.33 kHz / (255d - RC)

gives RC = 143.889, rounded to 144

Resolution = 1 /(255 - 144) = 1 / 111

Duty cycle desired: 37%

0.37 = (CP - 144) / (255 - 144) yields CP = 185.07, rounded to 185.

Summary: prescaler = 3, RC = 144d, CP = 185d: these numbers yield a PWM frequency of 12.012 kHz, a duty cycle of 36.94 % and a resolution of 0.9 %, which is very close to the initial goal.

#### Program example:

- SC0 is not programmed, so it keeps its reset value 00h (all flags cleared)

- The PWM signal starts as soon as the last instruction (ldi MC) is executed

#### **Program example**

| RC<br>CP<br>MC<br>SC0<br>SC1<br>LR | .def 0D9h,0FFh,0FFh<br>.def 0DAh,0FFh,0FFh<br>.def 0D5h,0FFh,0FFh<br>.def 0D6h,0FFh,0FFh<br>.def 0D7h,0FFh,0FFh<br>.def 0DBh,0FFh,0FFh | <pre>;reload/capture register ;compare register ;mode control register ;status/control register 0 ;status/control register 1 ;load register</pre> |

|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| ;=====                             | ldi CP, 185<br>ldi RC, 144<br>ldi SC1,001h                                                                                             | ;compare register = 185d<br>;reload register = 144d<br>;clock source= CPU clock divided by 3<br>;prescaler ratio = 1                              |

|                                    | ldi MC, 11100000b                                                                                                                      | ;auto-reload mode,interrupts disabled<br>;PWMOUT enabled, start timer                                                                             |

# Example 2:

Target: generate a PWM signal of frequency 31.3 kHz with a duty cycle proportional to an input analog voltage varying between 0V and  $V_{CC}$ : 0v corresponds to 0% duty cycle,  $V_{CC}$  corresponds to 100% duty cycle. The CPU clock is 8 MHz:

Referring to example 1, we find that the prescaler ratio must be 1, the value in RC must be 0 and the value in CP is taken directly from the A/D output (varying from 0 to 255d depending upon the analog input):

$\begin{array}{l} RC = 0 \\ CP = 0...255d \\ prescaler ratio = 1 \\ F_{IN} = 8 \; MHz \\ F_{PWM} = 8 \; MHZ \, / \, 255 = 31.37 \; kHz \\ Duty \; cycle = CP \, / \, 255d \\ Resolution = 1 / 255d = 0.39 \; \% \end{array}$

We need to implement a software loop which repetitively converts the analog input to a digital value and copies this digital value into CP:

#### **Program example**

| A                                                                     | .def 0FFh,0FFh,0FFh                                                                                                                    | ;Accumulator                                                                                                                                                          |  |  |

|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ;************* Port Register Set ***********************************  |                                                                                                                                        |                                                                                                                                                                       |  |  |

| PA<br>PADIR<br>PAOPT<br>;*******                                      | .def 0C0h,0FFh,0FFh<br>.def 0C4h,0FFh,0FFh<br>.def 0CCh,0FFh,0FFh                                                                      | ;Data Register Port A<br>;Data Direction Reg. Port A<br>;Option Register Port A<br>Set *********************                                                          |  |  |

| RC<br>CP<br>MC<br>SC0<br>SC1<br>LR                                    | .def 0D9h,0FFh,0FFh<br>.def 0DAh,0FFh,0FFh<br>.def 0D5h,0FFh,0FFh<br>.def 0D6h,0FFh,0FFh<br>.def 0D7h,0FFh,0FFh<br>.def 0DBh,0FFh,0FFh | <pre>;reload capture register<br/>;compare Register<br/>;mode control register<br/>;status control register 0<br/>;status control register 1<br/>;load register</pre> |  |  |

| ;*************** ADC Register Set *********************************** |                                                                                                                                        |                                                                                                                                                                       |  |  |

| ADCC<br>ADC                                                           | .def 0D1h,0FFh,0FFh<br>.def 0D0h,0FFh,0FFh                                                                                             | ;adc control register<br>;adc result Register                                                                                                                         |  |  |

| ;*********** MAIN ************************************                |                                                                                                                                        |                                                                                                                                                                       |  |  |

| ;port A must be an IOP3 type (port with analog input mode):           |                                                                                                                                        |                                                                                                                                                                       |  |  |

|                                                                       | ldi PADIR,000h<br>ldi PAOPT,001h<br>ldi PA, 001h                                                                                       | ;PA0 is the analog input<br>;PA1PA7 are input with pull-up                                                                                                            |  |  |

|                                                                       | ldi SC1,00000000b<br>ldi CP,07fh                                                                                                       | ;PSC divides by 1<br>;compare register = 127d<br>;(initial duty = 50%)                                                                                                |  |  |

|                                                                       | ldi RC,000h                                                                                                                            | ;reload register = 0                                                                                                                                                  |  |  |

|                                                                       | ldi MC,11100000b                                                                                                                       | ;(count up from 0 to 255)<br>;auto-reload mode,interrupt disabled<br>;PWMOUT enabled, start timer with<br>;duty cycle 50% at start-up                                 |  |  |

| adc_loop                                                              |                                                                                                                                        |                                                                                                                                                                       |  |  |

| wt oog                                                                | ldi ADCC,030h                                                                                                                          | ;start A/D conversion                                                                                                                                                 |  |  |

| wt_eoc                                                                | jrr 6,ADCC,wt_eoc<br>ld A,ADC<br>ld CP,A<br>jp adc_loop                                                                                | ;wait for end-of-conversion<br>;save result into Accumulator<br>;copy it into CP register<br>;do it again                                                             |  |  |

|                                                                       |                                                                                                                                        |                                                                                                                                                                       |  |  |

The length of the loop "adc\_loop" is the interval at which the duty cycle of the PWM signal will be updated. In this example, this loop lasts around 76µs, so the PWM duty cycle is updated every 2 or 3 PWM cycles. Calculation of the 80µs:

- Instructions ldi, ld and jp last 4 cycles of 13 clock periods -> 4 x 4 x 13 8MHz periods = 26 µs

- Instruction jrr lasts as long as the A/D takes to convert, which is around 50µs at 8MHz -> total length of adc\_loop at 8 MHz = approx. 76µs

This last example shows that, as requested, the CPU is not used to generate the PWM signal, but only to start/stop it and to update the duty cycle.

THE SOFTWARE INCLUDED IN THIS NOTE IS FOR GUIDANCE ONLY. SGS-THOMSON SHALL NOT BE HELD LIABLE FOR ANY DIRECT, INDIRECT OR CONSEQUENTIAL DAMAGES WITH RESPECT TO ANY CLAIMS ARISING FROM USE OF THE SOFTWARE.

Information furnished is believed to be accurate and reliable. However, SGS-THOMSON Microelectronics assumes no responsability for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of SGS-THOMSON Microelectronics. Specificationsmentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied.

SGS-THOMSON Microelectronics products are not authorized for use as critical components in life support devices or systems without the express written approval of SGS-THOMSON Microelectronics.

© 1994 SGS-THOMSON Microelectronics - All rights reserved.

Purchase of I<sup>2</sup>C Components by SGS-THOMSON Microelectronics conveys a license under the Philips I<sup>2</sup>C Patent. Rights to use these components in an I<sup>2</sup>C system is granted provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

SGS-THOMSON Microelectronics Group of Companies

Australia - Brazil - France - Germany - Hong Kong - Italy - Japan - Korea - Malaysia - Malta - Morocco - The Netherlands Singapore - Spain - Sweden - Switzerland - Taiwan - Thailand - United Kingdom - U.S.A.